SPERRY RAND

# UNIVAC

IIO8

MULTI-PROCESSOR

SYSTEM

PROCESSOR AND STORAGE

PROGRAMMERS REFERENCE This manual is published by the Univac Division of Sperry Rand Corporation in loose leaf format. This format provides a rapid and complete means of keeping recipients apprised of UNIVAC® Systems developments. The information presented herein may not reflect the current status of the product. For the current status of the product, contact your local Univac Representative.

The Univac Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of hardware or software changes and refinements. The Univac Division reserves the right to make such additions, corrections, and/or deletions as, in the judgment of the Univac Division, are required by the development of its Systems.

UNIVAC is a registered trademark of Sperry Rand Corporation.

Other trademarks of Sperry Rand Corporation appearing in the text of this publication are:

PAGEWRITER

## CONTENTS

| CONTENTS                                                                                                                                                                                       |                                                                   | 1 to 12                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|

| 1. INTRODUCTION 1.1. GENERAL                                                                                                                                                                   |                                                                   | 1-1 to 1-4<br>1-1                             |

| 1.2. UNIVAC 1108 MULT                                                                                                                                                                          | I-PROCESSOR SYSTEM                                                | 1-1                                           |

| 1.3. SYSTEM COMPONE 1.3.1. Processor Group 1.3.2. Storage Group 1.3.3. Multi-Module Acce 1.3.4. Input/Output Cont 1.3.5. Availability Contro 1.3.6. Shared Peripheral 1.3.7. Peripheral Subsys | ss Unit (MMA)<br>roller (IOC)<br>ol Unit (ACU)<br>Interface (SPI) | 1-1<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-4 |

| 2. PROCESSOR UNIT                                                                                                                                                                              |                                                                   | 2-1 to 2-2                                    |

| 2.1. GENERAL                                                                                                                                                                                   |                                                                   | 2-1                                           |

| 2.2. CONTROL SECTION 2.2.1. Control Section Op 2.2.2. Instruction Repert 2.2.3. Control Registers                                                                                              | peration                                                          | 2-1<br>2-1<br>2-1<br>2-1                      |

| 2.3. ARITHMETIC SECT                                                                                                                                                                           | ION                                                               | 2-2                                           |

| 2.4. INPUT/OUTPUT SE                                                                                                                                                                           | CTION                                                             | 2-2                                           |

PAGE:

| 3. | STORAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-1 to 3-13                                                                                                                                          |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 3.1. GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-1                                                                                                                                                  |

|    | 3.2. MAIN STORAGE 3.2.1. Addressing Main Storage 3.2.1.1. Noninterleaved Addressing of Main Storage 3.2.1.2. Interleaved Addressing of Main Storage 3.2.2. Multi-Module Access Unit (MMA) 3.2.3. Main Storage Special Address Assignments 3.2.3.1 Hidden Storage 3.2.3.2. Fixed Address Assignments 3.2.4. Main Storage Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-1<br>3-1<br>3-1<br>3-2<br>3-3<br>3-7<br>3-7<br>3-7<br>3-9                                                                                          |

|    | <ul> <li>3.3. CONTROL REGISTERS</li> <li>3.3.1. Control Register Selection Designator</li> <li>3.3.2. Control Register Address Assignments</li> <li>3.3.2.1. Temporary Storage for Processor State Register (PSR) at Interrupt - Address 000<sub>8</sub></li> <li>3.3.2.2. User Index (X) Registers - Addresses 001<sub>8</sub> - 017<sub>8</sub></li> <li>3.3.2.3. User Accumulator (A) Registers - Addresses 014<sub>8</sub> - 033<sub>8</sub></li> <li>3.3.2.4. User Unassigned Registers - Addresses 034<sub>8</sub> - 037<sub>8</sub></li> <li>3.3.2.5. Input/Output Access Control Registers - Addresses 040<sub>8</sub> -077<sub>8</sub></li> <li>3.3.2.6. Real Time Clock (R0) Register - Address 100<sub>8</sub></li> <li>3.3.2.7. User Repeat Count (R1) Register - Address 101<sub>8</sub></li> <li>3.3.2.8. User Mask (R2) Register - Address 102<sub>8</sub></li> <li>3.3.2.9. User R Registers - Addresses 103<sub>8</sub> - 117<sub>8</sub></li> <li>3.3.2.10. Executive R Register - Address 120<sub>8</sub></li> <li>3.3.2.11. Executive Repeat Count (R1) Register - Address 121<sub>8</sub></li> <li>3.3.2.12. Executive Mask (R2) Register - Addresses 123<sub>8</sub> - 137<sub>8</sub></li> <li>3.3.2.13. Executive R Registers - Addresses 123<sub>8</sub> - 137<sub>8</sub></li> <li>3.3.2.14. Executive Nonindexing X Register - Addresses 141<sub>8</sub> - 157<sub>8</sub></li> <li>3.3.2.15. Executive Index (X) Registers - Addresses 154<sub>8</sub> - 173<sub>8</sub></li> <li>3.3.2.16. Executive Unassigned Registers - Addresses 174<sub>8</sub> - 177<sub>8</sub></li> <li>3.3.2.17. Executive Unassigned Registers - Addresses 174<sub>8</sub> - 177<sub>8</sub></li> <li>3.3.3. Control Register Protection</li> </ul> | 3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-11<br>3-11<br>3-12<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13 |

| 4. | CPU ARITHMETIC SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1 to 4-38                                                                                                                                          |

|    | 4.1. GENERAL OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1                                                                                                                                                  |

|    | <ul><li>4.2. MAIN ADDER</li><li>4.2.1. Signed Numbers</li><li>4.2.2. Zero as a Signed Number</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-1<br>4-4<br>4-4                                                                                                                                    |

|    | 4.3. FIXED-POINT ARITHMETIC 4.3.1. Single-Precision Fixed-Point Addition and Subtraction 4.3.2. Double-Precision Fixed-Point Addition and Subtraction 4.3.3. Fixed-Point Overflow and Carry 4.3.3.1. Overflow 4.3.3.2. Carry 4.3.4. Fixed-Point Multiplication 4.3.5. Fixed-Point Division 4.3.6. Divide Fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-7<br>4-8<br>4-10<br>4-12                                                                                        |

| 4.4. FLOATING-POINT ARITHMETIC                                                                                                                  | 4-13         |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 4.4.1. Floating-Point Formats                                                                                                                   | 4-13         |

| 4.4.1.1. Positive Single-Precision Floating-Point Numbers                                                                                       | 4-15         |

| 4.4.1.2. Positive Double-Precision Floating-Point Numbers                                                                                       | 4-16         |

| 4.4.1.3. Negative Floating-Point Numbers                                                                                                        | 4-16         |

| 4.4.1.4. Residue                                                                                                                                | 4-17         |

| 4.4.2. Normalized/Unnormalized Floating-Point Numbers                                                                                           | 4-17         |

| 4.4.3. Floating-Point Characteristic Overflow/Underflow                                                                                         | 4-18         |

| 4.4.3.1. Floating-Point Characteristic Overflow                                                                                                 | 4-18         |

| 4.4.3.2. Floating-Point Characteristic Underflow                                                                                                | 4-18<br>4-19 |

| 4.4.4. Mechanics of Floating-Point Arithmetic                                                                                                   | 4-19<br>4-19 |

| 4.4.4.1. Floating-Point Addition 4.4.4.1.1. Single-Precision Floating-Point Addition                                                            | 4-19         |

| 4.4.4.1.2. Single-Precision Floating-Point Addition — Special Cases                                                                             | 4-13         |

| 4.4.4.1.3. Double-Precision Floating-Point Addition                                                                                             | 4-22         |

| 4.4.4.2. Floating-Point Add Negative (Subtraction)                                                                                              | 4-24         |

| 4.4.4.3. Floating-Point Multiplication                                                                                                          | 4-24         |

| 4.4.4.3.1. Single-Precision Floating-Point Multiplication                                                                                       | 4-25         |

| 4.4.4.3.2. Double-Precision Floating-Point Multiplication                                                                                       | 4-27         |

| 4.4.4.4. Floating-Point Division                                                                                                                | 4-29         |

| 4.4.4.4.1. Single-Precision Floating-Point Division                                                                                             | 4-29         |

| 4.4.4.2. Double-Precision Floating-Point Division                                                                                               | 4-31         |

|                                                                                                                                                 |              |

| 4.5. CONVERTING A FIXED-POINT NUMBER TO A FLOATING-POINT NUMBER                                                                                 | 4-33         |

| 4.5.1. Conversion To Single-Precision Floating-Point Format                                                                                     | 4-33         |

| 4.5.2. Conversion To Double-Precision Floating-Point Format                                                                                     | 4-35         |

| A.C. ELOATINO DOINT ZEDO CUMMADV                                                                                                                | 4 2C         |

| 4.6. FLOATING-POINT ZERO – SUMMARY                                                                                                              | 4-36         |

| 4.6.1. Single-Precision Floating-Point Zero                                                                                                     | 4-36         |

| 4.6.2. Double-Precision Floating-Point Zero                                                                                                     | 4-38         |

| CPU CONTROL SECTION                                                                                                                             | 5-1 to 5-29  |

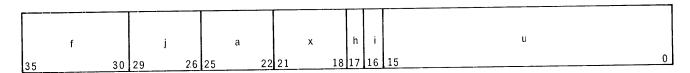

| 5.1. INSTRUCTION WORD FORMAT                                                                                                                    | 5-1          |

|                                                                                                                                                 | 0 1          |

| 5.2. INSTRUCTION WORD FIELDS                                                                                                                    | 5-2          |

| 5.2.1. Description of f Field                                                                                                                   | 5-2          |

| 5.2.2. Description of j Field                                                                                                                   | 5-2          |

| 5.2.2.1. j Field as an Operand Qualifier                                                                                                        | 5-2          |

| 5.2.2.1.1. Operand Qualification for Store and Block Transfer Instructions                                                                      | 5-5          |

| 5.2.2.1.2. Operand Qualification When $f = 10_8$ Through $67_8$                                                                                 | 5-5          |

| 5.2.2.2. Use of j Field as Partial Control Register Address                                                                                     | 5-5          |

| 5.2.2.3. Use of j Field as Minor Function Code                                                                                                  | 5-6          |

| 5.2.3. Description of a Field                                                                                                                   | 5-6          |

| 5.2.3.1. Use of the a Field to Reference A Register                                                                                             | 5-6          |

| 5.2.3.2. Use of the a Field to Reference X Registers                                                                                            | 5-6          |

| 5.2.3.3. Use of the a Field to Reference R Register                                                                                             | 5-7          |

| 5.2.3.4. Use of the a Field to Reference I/O Channels                                                                                           | 5-7          |

| 5.2.3.5. Use of the a Field to Reference Jump Keys                                                                                              | 5-7          |

| 5.2.3.6. Use of the a Field to Reference Halt Keys                                                                                              | 5-7          |

| <ul><li>5.2.3.7. Use of the a Field to Modify Memory Select Register (MSR)</li><li>5.2.3.8. Use of the a Field as Minor Function Code</li></ul> | 5-7<br>5-7   |

|                                                                                                                                                 | n /          |

5.

Contents

PAGE:

SECTION:

6 - 5

UNIVAC 1108

6.2.11. Double Load Magnitude A

PROCESSOR AND STORAGE

UP-4053

Rev. 1

| 6.3. STORE INSTRUCTIONS 6.3.1. Store A 6.3.2. Store Negative A 6.3.3. Store Magnitude A 6.3.4. Store R 6.3.5. Store Zero 6.3.6. Store X 6.3.7. Double Store A 6.3.8. Block Transfer                                                                                                                                                                                                                                                                                                                                                                                                                | 6-5<br>6-5<br>6-6<br>6-6<br>6-6<br>6-7<br>6-7                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 6.4. FIXED-POINT ARITHMETIC INSTRUCTIONS 6.4.1. Add to A 6.4.2. Add Negative to A 6.4.3. Add Magnitude to A 6.4.4. Add Negative Magnitude to A 6.4.5. Add Upper 6.4.6. Add Negative Upper 6.4.7. Add to X 6.4.8. Add Negative to X 6.4.9. Multiply Integer 6.4.10. Multiply Single Integer 6.4.11. Multiply Fractional 6.4.12. Divide Integer 6.4.13. Divide Single Fractional 6.4.14. Divide Fractional 6.4.15. Double-Precision Fixed Point Add 6.4.16. Double-Precision Fixed Point Add 6.4.17. Add Halves 6.4.18. Add Negative Halves 6.4.19. Add Thirds                                       | 6-9 6-10 6-10 6-11 6-11 6-12 6-12 6-13 6-13 6-14 6-15 6-15 6-16 6-17 6-17 6-18 6-18                                  |

| 6.5. FLOATING-POINT ARITHMETIC 6.5.1. Floating Add 6.5.2. Floating Add Negative 6.5.3. Double-Precision Floating Add Negative 6.5.4. Double-Precision Floating Add Negative 6.5.5. Floating Multiply 6.5.6. Double-Precision Floating Multiply 6.5.7. Floating Divide 6.5.8. Double-Precision Floating Divide 6.5.9. Load and Unpack Floating 6.5.10. Double Load and Unpack Floating 6.5.11. Load and Convert to Floating 6.5.12. Double Load and Convert to Floating 6.5.13. Floating Expand and Load 6.5.14. Floating Compress and Load 6.5.15. Magnitude of Characteristic Difference to Upper | 6-19<br>6-20<br>6-20<br>6-21<br>6-21<br>6-23<br>6-23<br>6-25<br>6-26<br>6-26<br>6-27<br>6-27<br>6-28<br>6-29<br>6-30 |

| 6.5.16. Characteristic Difference to Upper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-30                                                                                                                 |

UP-4053 UNIVAC 1108 Contents

Rev. 1 PROCESSOR AND STORAGE SECTION: PAGE:

| 6.6. SEARCH AND MASKED SEARCH INSTRUCTIONS 6.6.1. Search Equal 6.6.2. Search Not Equal 6.6.3. Search Less than or Equal (SLE) — Search Not Greater (SNG) 6.6.4. Search Greater 6.6.5. Search Within Range 6.6.6. Search Not Within Range 6.6.7. Mask Search Equal 6.6.8. Mask Search Not Equal 6.6.9. Mask Search Less Than or Equal (MSLE) — Mask Search Not             | 6-30<br>6-33<br>6-34<br>6-35<br>6-36<br>6-37<br>6-38<br>6-39<br>6-40                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Greater (MSNG) 6.6.10. Mask Search Greater 6.6.11. Masked Search Within Range 6.6.12. Masked Search Not Within Range 6.6.13. Masked Alphanumeric Search Less Than or Equal 6.6.14. Masked Alphanumeric Search Greater                                                                                                                                                     | 6-41<br>6-42<br>6-42<br>6-44<br>6-45<br>6-46                                         |

| 6.7. TEST (OR SKIP) INSTRUCTIONS<br>6.7.1. Test Even Parity<br>6.7.2. Test Odd Parity<br>6.7.3. Test Less Than or Equal to Modifier (TLEM) — Test Not Greater                                                                                                                                                                                                             | 6-47<br>6-47<br>6-48                                                                 |

| Than Modifier (TNGM) 6.7.4. Test Zero 6.7.5. Test Nonzero 6.7.6. Test Equal 6.7.7. Test Not Equal 6.7.8. Test Less Than or Equal (TLE) – Test Not Greater (TNG) 6.7.9. Test Greater                                                                                                                                                                                       | 6-48<br>6-49<br>6-49<br>6-50<br>6-50<br>6-51<br>6-51                                 |

| 6.7.10. Test Within Range 6.7.11. Test Not Within Range 6.7.12. Test Positive 6.7.13. Test Negative 6.7.14. Double-Precision Test Equal                                                                                                                                                                                                                                   | 6-52<br>6-52<br>6-53<br>6-53<br>6-54                                                 |

| 6.8. SHIFT INSTRUCTIONS 6.8.1. Single Shift Circular 6.8.2. Double Shift Logical 6.8.3. Single Shift Logical 6.8.4. Double Shift Logical 6.8.5. Single Shift Algebraic 6.8.6. Double Shift Algebraic 6.8.7. Load Shift and Count 6.8.8. Double Load Shift and Count 6.8.9. Left Single Shift Circular 6.8.10. Left Double Shift Logical 6.8.11. Left Single Shift Logical | 6-54<br>6-56<br>6-57<br>6-57<br>6-57<br>6-58<br>6-58<br>6-59<br>6-59<br>6-60<br>6-60 |

| 6.9. UNCONDITIONAL JUMP INSTRUCTION 6.9.1. Store Location and Jump 6.9.2. Load Modifier and Jump 6.9.3. Allow All I/O Interrupts and Jump                                                                                                                                                                                                                                 | 6-61<br>6-62<br>6-63                                                                 |

6.13.1. Load Input Channel

6.13.2. Load Input Channel and Monitor

6.13.6. Load Output Channel and Monitor

6.13.10. Load Function in Channel and Monitor

6.13.12. Prevent all Channel External Interrupts

6.13.13. Allow all Channel External Interrupts

6.13.7. Jump on Output Channel Busy 6.13.8. Disconnect Output Channel

6.13.11. Jump on Function in Channel

6.13.3. Jump on Input Channel Busy

6.13.4. Disconnect Input Channel

6.13.5. Load Output Channel

6.13.9. Load Function Channel

7

PAGE:

6-77

6-77

6 - 77

6 - 78

6 - 78

6 - 79

6 - 79

6 - 80

6 - 80

6 - 81

6 - 81

6 - 82

6-82

PAGE:

Contents

SECTION:

7 - 27

7 - 28

7 - 31

**UNIVAC 1108**

PROCESSOR AND STORAGE

7.2.11.1. ISI Function Mode Programming Considerations

7.2.11.2. ISI Output Mode Programming Considerations

7.2.11.3. ISI Input Mode Programming Considerations

UP-4053

Rev. 1

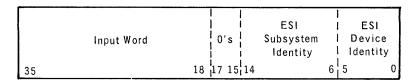

| 7.3. ESI MODE — I/O OPERATION 7.3.1. General Description — Operation of an I/O Channel in ESI Mode 7.3.2. ESI Word Format 7.3.3. ESI ACW Formats 7.3.3.1. ESI Half Word ACW Format 7.3.3.2. ESI Quarter Word ACW Format 7.3.4. ESI ACW Terminal Condition Detection 7.3.5. ESI Mode — Input/Output Channel Activity 7.3.5.1. ESI Mode — Function Word Transmission Activity 7.3.5.2. ESI Output Mode 7.3.5.3. ESI Input Mode 7.3.6. ESI Mode — I/O Channel Activity — ACW Initially in Terminal Condition 7.3.7. ESI Mode Monitor Interrupts 7.3.8. Programmed Deactivation of an I/O Channel in ESI Mode 7.3.9. Summary of I/O Channel Control Circuit Operation — ESI Mode 7.3.10. Summary of the CPU's Operation Versus the EI, IDR, and ODR Control Signals 7.3.11. I/O Programming Considerations — ESI Mode 7.3.11.1. ESI Function Word Transfer Programming Considerations 7.3.11.2. ESI Output Word Transfer Programming Considerations 7.3.11.3. ESI Input/Output Timing | 7-33 7-34 7-35 7-36 7-37 7-40 7-41 7-41 7-42 7-44 7-46 7-46 7-47 7-48 7-48 7-49 7-50 7-51 7-52 7-53                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-1 to 8-22                                                                                                                                              |

| 8.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-1                                                                                                                                                      |

| 8.2. I/O INTERRUPTS 8.2.1. Monitor Interrupts 8.2.1.1. ISI Input Monitor Interrupt 8.2.1.2. ISI Output Monitor Interrupt 8.2.1.3. ISI Function Monitor Interrupt 8.2.1.4. ESI Input Monitor Interrupt 8.2.1.5. ESI Output Monitor Interrupt 8.2.2. External Interrupts 8.2.2.1. ISI External Interrupt 8.2.2.2. ESI External Interrupt 8.2.3. System I/O Interrupt 8.2.3.1. Interprocessor Interrupt 8.2.3.2. Real Time Clock Interrupt 8.2.3.3. Day Clock Interrupt 8.2.3.4. Power Loss Interrupt 8.2.4. I/O Parity Error Interrupts 8.2.4.1. ESI Access Control Word Parity Error Interrupt 8.2.4.2. ISI Access Control Word Parity Error Interrupt 8.2.4.3. I/O Data Parity Error Interrupt 8.2.5. I/O Interrupt Priority                                                                                                                                                                                                                                                      | 8-2<br>8-3<br>8-3<br>8-3<br>8-4<br>8-4<br>8-4<br>8-5<br>8-6<br>8-6<br>8-6<br>8-7<br>8-7<br>8-7<br>8-7<br>8-8<br>8-8<br>8-8<br>8-8<br>8-9<br>8-10<br>8-12 |

Contents

9 - 16

9 - 16

9 - 16

10

PAGE:

UNIVAC 1108

9.4.1. Format for the Storage Limits Word

9.4.2. Loading the Storage Limits Register

9.4.3. Activating and Deactivating Main Storage Protection

UP-4053

Rev. 1

UP-4053 UNIVAC 1108 Contents Rev. 1

PROCESSOR AND STORAGE SECTION:

PAGE:

APPENDIXES

| Α.  | SYM    | BOLS AND ABBREVIATIONS                                                                        | A-1 to $A-7$ |

|-----|--------|-----------------------------------------------------------------------------------------------|--------------|

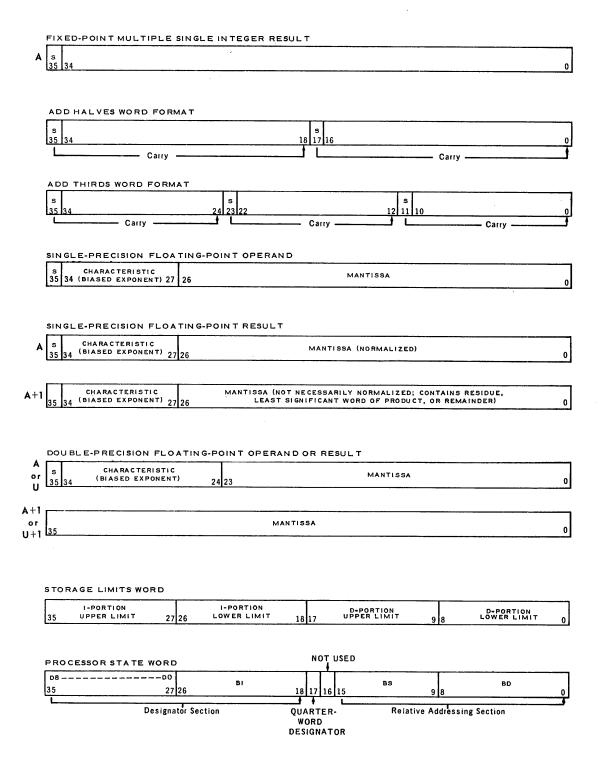

| в.  | UNIV   | AC 1108 WORD FORMATS                                                                          | B-1 to B-2   |

| c.  | CHAI   | RACTER CODES                                                                                  | C-1 to C-2   |

| D,  | PRO    | CESSOR UNIT DIFFERENCES                                                                       | D-1 to D-1   |

| E.  | INST   | RUCTION REPERTOIRE                                                                            | E-1 to E-11  |

| FIC | GURES  | 3                                                                                             |              |

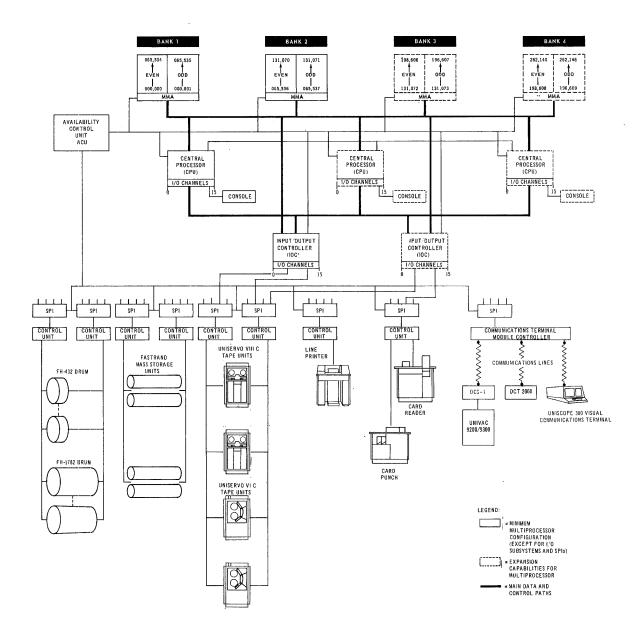

|     | 1-1.   | UNIVAC 1108 Multi-Processor System                                                            | 1-2          |

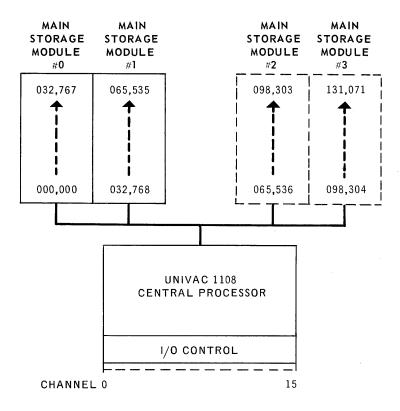

|     | 3-1.   | Central Processor Unit with Maximum Noninterleaved Main Storage                               | 3-2          |

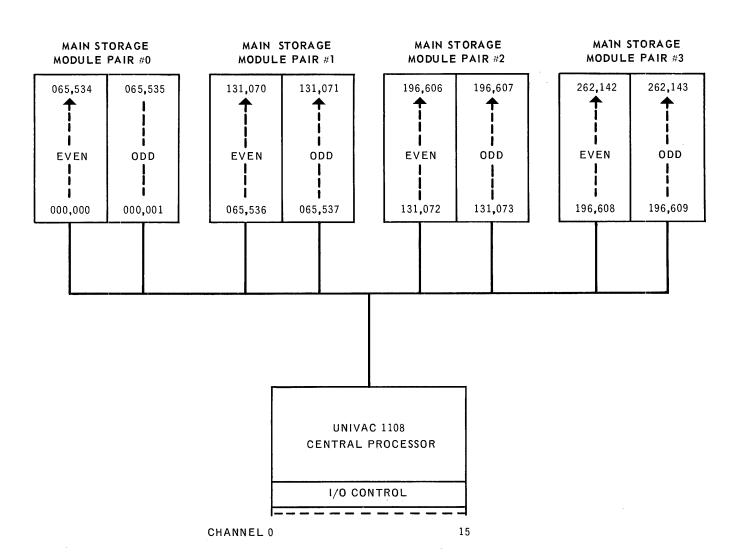

|     | 3-2.   | CPU with Maximum Interleaved Main Storage                                                     | 3-3          |

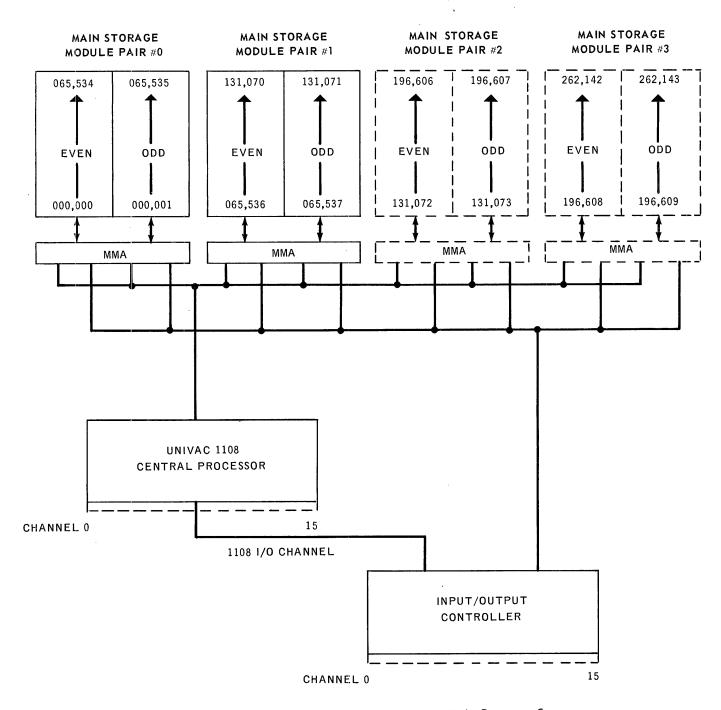

|     | 3-3.   | CPU, 10 C, and Main Storage with MMA's for UNIVAC 1108 Multi-Processor<br>System              | 3-4          |

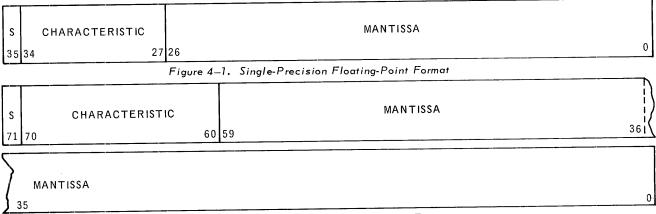

|     | 4-1.   | Single-Precision Floating-Point Format                                                        | 4-13         |

|     | 4-2.   | Double-Precision Floating-Point Format                                                        | 4-13         |

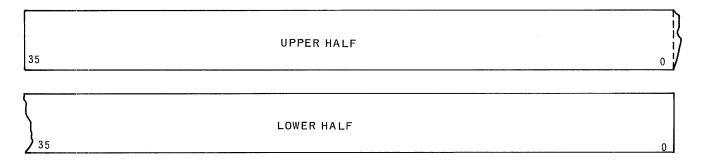

|     | 4-3.   | Nonaddressable 72-Bit Arithmetic Accumulator                                                  | 4-20         |

|     | 5-3.   | Transfers from Main Storage to the Arithmetic Section (f = $10_8$ through $67_8$ )            | 5 3          |

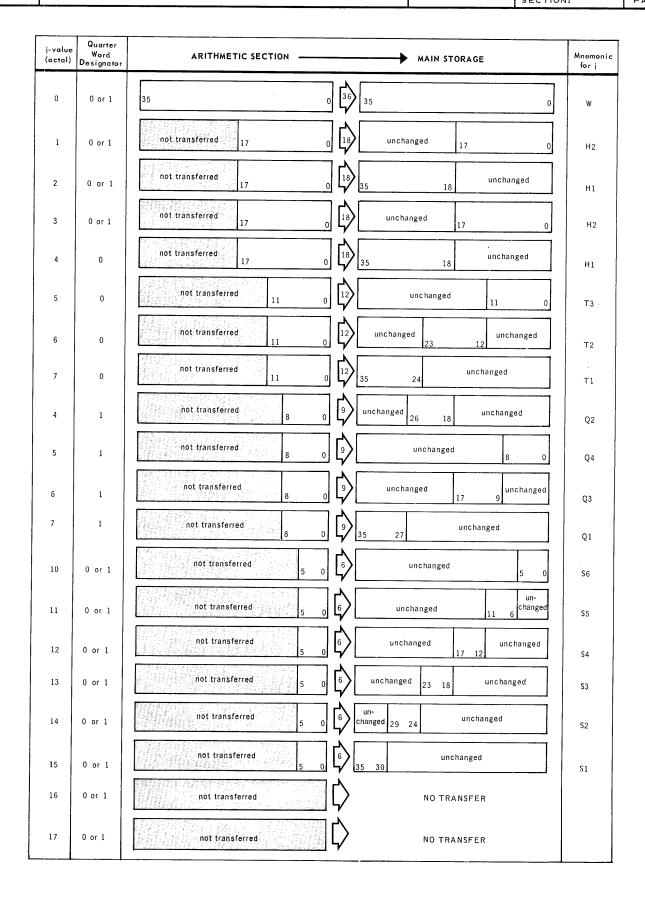

|     | 5-2.   | Transfers from the Arithmetic Section to Main Storage (f = $01_8$ through $06_8$ and $22_8$ ) | 5-4          |

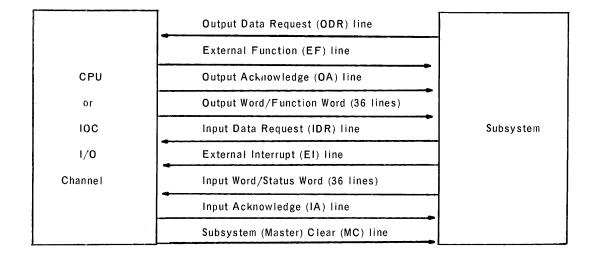

|     | 7-1.   | I/O Channel Interface, Control and Data Lines                                                 | 7-1          |

|     | 7-2.   | I/O Word Transfer Priority — Normal Channels Only                                             | 7-8          |

|     | 7 – 3. | I/O Word Transfer Priority - Compatible Channels Only                                         | 7-9          |

|     | 9-1.   | Format of the Processor State Word                                                            | 9 - 1        |

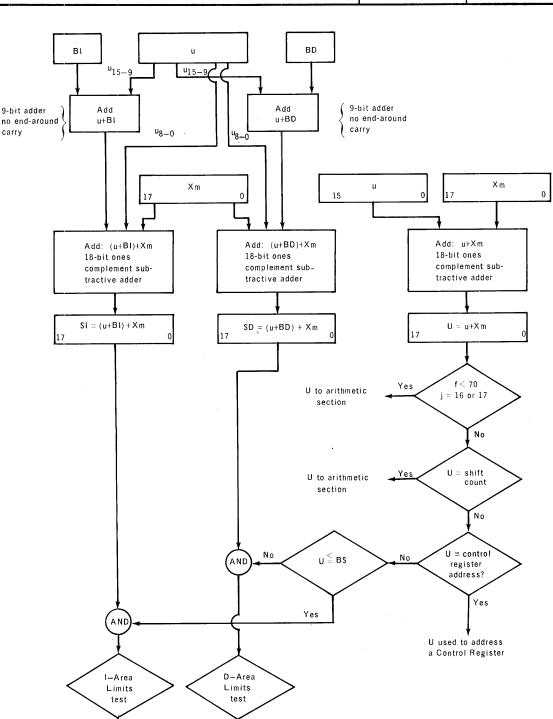

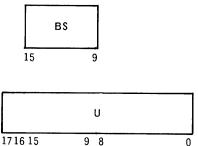

|     | 9-2.   | UNIVAC 1108 Addressing Operation Flowchart                                                    | 9 - 4        |

| TA  | BLES   |                                                                                               |              |

|     | 3-1.   | Octal and Decimal Address Ranges for Noninterleaved Main Storage Modules                      | 3-1          |

|     | 3-2.   | Octal and Decimal Address Ranges for Interleaved Main Storage Modules                         | 3-3          |

|     | 3-3.   | Main Storage Fixed Address Assignments                                                        | 3-8          |

|     | 3-4.   | MSR Values vs. Module Pair Identification for Noninterleaved Main Storage                     | 3-9          |

|     | 3-5.   | MSR Values vs. Module Pair Identification for Interleaved Main Storage                        | 3-9          |

|     | 3-6.   | Control Register Address Assignments                                                          | 3-10         |

| 4-1. | Sign Bit Combinations Which Set Overflow Designator                                       | 4-7  |

|------|-------------------------------------------------------------------------------------------|------|

| 4-2. | Sign Bit Combinations Which Set Carry Designator                                          | 4-8  |

| 4-3. | Single-Precision Floating-Point Characteristic Values vs. Exponent Values                 | 4-14 |

| 4-4. | Double-Precision Floating-Point Characteristic Values vs. Exponent Values                 | 4-14 |

| 4-5. | Instructions Producing Results In Single-Precision Floating-Point Format                  | 4-36 |

| 5-1. | Use of i Field                                                                            | 5-9  |

| 6-1. | Truth Table for Logical OR, XOR, and AND                                                  | 6-71 |

| 6-2. | Interprocessor Interrupt Relationships                                                    | 6-88 |

| 7-1. | I/O Channel, Control and Data Lines                                                       | 7-2  |

| 8-1. | I/O Request and Interrupt Priority Table                                                  | 8-12 |

| 8-2. | Main Storage or Control Register Parity Error Fault Interrupt<br>Locations and Priorities | 8-13 |

| 8-3. | UNIVAC 1108 Interrupt Versus P Register Contents Captured                                 | 8-21 |

| 9-1. | The Range of Block Numbers for Noninterleaved and Interleaved Main Storage                | 9-8  |

| E-1. | Instruction Repertoire                                                                    | E-1  |

| E-2. | Mnemonic/Function Code Cross-Reference                                                    | E-11 |

## 1. INTRODUCTION

#### 1.1. GENERAL

This manual provides information on the UNIVAC 1108 Central Processor Unit (CPU), the Multi-Module Access Unit, and the Storage Unit (main storage) of the UNIVAC 1108 Multi-Processor System.

#### 1.2. UNIVAC 1108 MULTI-PROCESSOR SYSTEM

The UNIVAC 1108 Multi-Processor System is the logical successor to the UNIVAC 1107 Thin-Film Memory Computer. It has higher speeds, larger capacities, increased versatility, and smaller physical size than the UNIVAC 1107 System.

Two prime objectives of a multiprocessor system are:

- Increased system performance

- Increased system availability

The UNIVAC 1108 Multi-Processor System achieves increased performance by using multiple processing units, multiple input/output units, and multiple access paths to critical peripheral devices.

Increased availability is achieved by providing multiple access paths to all system components, and by permitting the removal of any system component for offline testing and maintenance while the online units continue to operate.

A UNIVAC 1108 Multi-Processor System includes from one to three Central Processor Units (CPU) and one or two Input/Output Controllers (IOC). In those systems having more than one CPU, the CPU's may operate simultaneously and independently of each other, but they are coordinated by a single Executive program. A system consisting of only one CPU and no IOC is referred to as a Unit Processor System.

Figure 1-1 is a simplified diagram of a UNIVAC 1108 Multi-Processor System. Primary units are four Storage Units, three CPU's, two IOC's, and the Availability Control Unit (ACU). Some of the other possible system configurations are presented and discussed in Section 3.

#### 1.3. SYSTEM COMPONENTS

The components of a UNIVAC 1108 Multi-Processor System are as follows:

■ Processor Group

Type No. 3011-95

■ Multiprocessor Capability

Feature No. 1053-99

■ Storage Group

Type No. 7005-72 (131K) 7005-71 (196K)

7005-70 (262K)

■ Multi-Module Access Unit (MMA) Type No. 0954-99

■ I/O Controller (IOC)

Type No. 5013-00

■ Availability Control Unit (ACU) Type No. 2506-00

- Shared Peripheral Interface (SPI) Type No. 0955-04

- Peripheral Subsystems

Figure 1-1. UNIVAC 1108 Multi-Processor System

#### 1.3.1. Processor Group

The Processor Group consists of the following (each in a separate cabinet):

- Central Processor Unit (CPU)

- Power and Maintenance Cabinet

- Display Console

The CPU incorporates all features needed for operation in a multiprocessor environment. Each of the CPU's has full access to all of main storage through the Multi-Module Access Units (MMA's). Through its input/output (I/O) section, each CPU has full access to all I/O subsystems in the system.

The Display Console enables the operator to control and communicate with the operating system. Each CPU communicates with its console through I/O channel 15. Output from the CPU to the operator takes the form of messages displayed on a cathode-ray tube (CRT) display, and hardware status information is displayed on the operator's control panel. Operator to CPU communication and control is provided by the console keyboard, and the positioning of various conditioning and directing switches. A hard copy of the messages appearing on the CRT display is provided by a UNIVAC PAGEWRITER printer.

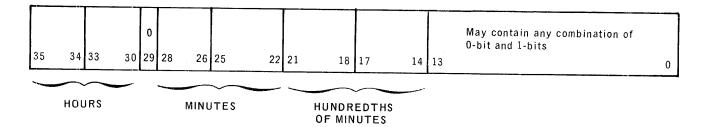

Each Display Console is equipped with a day clock which displays the time of day in hours, minutes, and hundredths of a minute. Storage of the day clock reading at a fixed location in main storage can be enabled or disabled, either manually or under program control. When enabled, the reading is updated 100 times per minute, and interrupts to the CPU are generated at six second intervals.

#### 1.3.2. Storage Group

The Storage Group may consist of from one to four cabinets, each of which houses a Storage Unit and power supply. A Storage Unit provides 65,536 words of main storage (36-bit words). The main storage cycle time is 750 nanoseconds.

By using hardware implemented interleaving for addressing, main storage is utilized more efficiently.

#### 1.3.3. Multi-Module Access Unit (MMA)

The MMA is the interface between a Storage Unit and the CPU's and IOC's in a UNIVAC 1108 Multi-Processor System. Each MMA is housed in a separate cabinet. A MMA includes two logically independent sections, each associated with one module (32K) of a Storage Unit. Each section is used by the CPU's and IOC's to request and receive access to the corresponding module of a Storage Unit. When a conflict occurs between two or more access requests, the MMA services the requests on a priority basis.

#### 1.3.4. Input/Output Controller (IOC)

The IOC is functionally similar to the I/O section of the CPU. The IOC may have up to 16 I/O channels and may be controlled by any of the CPU's in the system. A CPU sends commands to the IOC; this action initiates I/O data transfers under control of the IOC. The data transfers between the subsystems and main storage take place independently of the CPU. When the IOC completes an I/O operation, it signals I/O termination to the CPU. All command and data transfers between the CPU and IOC utilize the CPU's I/O channel interface. The IOC further enhances the system performance by providing chained-buffer (scatter-read/gather-write) operation, and by permitting a more efficient Externally Specified Index (ESI) mode of operation.

One or two IOC's may be included in a UNIVAC 1108 Multi-Processor System. For additional information on the IOC see UNIVAC 1108 Multi-Processor System Input/ Output Controller Programmer/Operator Reference Manual, UP-7514 (current version).

#### 1.3.5. Availability Control Unit (ACU)

The ACU provides complete configuration control of the UNIVAC 1108 Multi-Processor system. It interfaces with the CPU's, IOC's, Storage Units, and MMA's for up to 24 peripheral subsystems. The ACU provides the means for:

- dividing the overall system into independent systems;

- disabling the CPU's or IOC's whenever a power fault occurs;

- taking a unit offline for maintenance without interfering with the operation of the remainder of the system;

- initiating an automatic recovery sequence in the event of system failure; and

- indicating to the CPU which units are online and available.

#### 1.3.6. Shared Peripheral Interface (SPI)

The SPI enables several processors to control a single peripheral subsystem. It is an electronic switching device through which two, three, or four processors (CPU's or IOC's) in any combination can share a peripheral subsystem. Certain peripheral subsystems provide an interface which is functionally equivalent to a SPI.

Additional information on the SPI (formerly called Multiple Processor Adapter) can be found in UNIVAC 1108 Multi-Processor System Multiple Processor Adapter Programmer/Operator Reference Manual, UP-7562 (current version).

#### 1.3.7. Peripheral Subsystems

Various peripheral subsystems can be used with the UNIVAC 1108 Multi-Processor System. These subsystems include high speed printers, card readers and punches, magnetic tapes, magnetic drums, communication subsystems. In the UNIVAC 1108 Multi-Processor System, the subsystems can be accessed by all the CPU's by utilizing an IOC and/or SPI (or equivalent). A subsystem may also be directly connected to an I/O channel of a CPU. In this case, the subsystem is available only to that CPU.

## 2. PROCESSOR UNIT

#### 2.1. GENERAL

UP-4053

Rev. 1

The Central Processor Unit (CPU) is a solid-state, integrated-circuit, data processing unit which features a powerful and comprehensive instruction repertoire, addressable control registers, high speed arithmetic operations, and a versatile input/output (I/O) section.

#### 2.2. CONTROL SECTION

The control section of the CPU interprets instructions and directs all CPU operations except certain I/O operations. It is discussed briefly below and in more detail in Section 5.

#### 2.2.1. Control Section Operation

The program instruction words are sequentially loaded into the control section. Each instruction word is interpreted by the control section which generates the signals necessary to perform the instruction. The instruction words are located in main storage and the data words (operands) are located either in main storage or in the addressable control registers which are part of the CPU's control section. The control section includes a Program Address Counter (P register), which addresses main storage to obtain the instruction words.

The instruction word is divided into fields. These fields specify to the control section the function to be performed, which portion of the operand is to be used, a control register, indexing, index register modification, indirect addressing, and an operand address.

#### 2.2.2. Instruction Repertoire

The instruction repertoire is all the instructions that the control section of the CPU is capable of interpreting and executing. It includes fixed-point and floating-point arithmetic, logical functions, data transfers, block transfers, comparisons, tests, I/O control, and special purpose instructions. There are over 140 basic instructions in the repertoire. Provision has been made for partial word data transfers and for repetitive operations. Indexing capability is provided with all instructions. Indirect addressing capability is also provided and is usable to any level with full indexing capability at each level.

Instructions such as data transfers, single-precision fixed-point adds, certain logical functions, require only 750 nanoseconds for complete execution. Indexing does not add to the execution time of an instruction.

#### 2.2.3. Control Registers

The 128 addressable control registers of the control section are integrated-circuit registers. These control registers are addressed either explicitly or implicitly by the instructions. They fall into five categories: index registers, arithmetic registers, special registers, I/O access control registers, and unassigned registers.

The control registers are discussed in detail in 3.3 and Section 5.

#### 2.3. ARITHMETIC SECTION

All arithmetic computation is performed using the nonaddressable registers of the arithmetic section. These arithmetic processes can be performed in either fixed-point or floating-point mode. Fixed-point arithmetic instructions provide for single-precision, double-precision, half-word, and third-word addition and subtraction, and for fraction and integer multiplication and division. Floating-point instructions provide for both single-precision and double-precision operation. The arithmetic section also performs certain logical operations such as shifting and comparisons. The instruction word may be used to specify the transfer of any chosen portion of a word (half, third, quarter, or sixth) to or from the arithmetic section. The ability to transfer only the selected portion of a word minimizes the number of masking and shifting operations required.

A shift matrix in the arithmetic section permits the completion of an entire single word shift operation in one main storage cycle time. By use of the matrix, the shift operation can shift a single or double word operand in either direction up to 72 bit positions. Partial word transfers utilize automatic shifting operations in the shift matrix.

Details on the operation of the arithmetic section of the CPU are found in Section 4.

#### 2.4. INPUT/OUTPUT SECTION

The I/O section, while physically located in the CPU cabinet, is a functional entity. I/O activity is initiated when the interpretation of certain instructions by the control section causes signals to be sent to the I/O section. Once the I/O operation is initiated, the I/O section and the subsystem control the input and output transfers. The I/O section complements the control and arithmetic sections' orientation toward high speed concurrent program processing and real time operation. The I/O section operates with a wide variety of peripheral devices, and it requires minimal attention from the control section.

Once an I/O operation is initiated by the program, I/O activity is independent of program control and it is controlled by an I/O Access Control Word stored in a control register. The I/O data flows between the main storage and the peripheral subsystem through an I/O channel. Each I/O channel consists of 36 input data lines, 36 output data lines, and various control signal lines. All data word bits are transmitted in parallel to or from the subsystem, but data can flow in only one direction over a channel at any given instant.

The I/O section of a basic CPU includes eight I/O channels. An I/O Channel Expansion Feature (F0680) may be added to the CPU to increase the number of I/O channels from eight to 12. If 16 I/O channels are required, a second I/O Channel Expansion Feature must be added. The total number of I/O channels available to a CPU is expanded by the inclusion of one or two IOC's in the system.

Details on the input/output section of the CPU are presented in Section 7.

### 3. STORAGE

#### 3.1. GENERAL

The Storage Units of the UNIVAC 1108 Multi-Processor System provide the main storage for instruction and data words. The 128 addressable control registers in the control section of each Central Processor Unit (CPU) provide fast access storage for data and control words.

#### 3.2. MAIN STORAGE

A main storage word consists of 36 information bits and 2 parity bits. The two parity bits provide independent hardware parity checking of the leftmost 18 data bits and the rightmost 18 data bits of the main storage word, respectively. The word may be an instruction word, a data word, or an access control word.

A Storage Unit can store 65,536 words. Functionally, each Storage Unit is divided into two modules, with each module providing 32,768 words of main storage. Each module includes independent accessing circuitry which permits simultaneous accessing of multiple modules.

#### 3.2.1. Addressing Main Storage

Main storage addressing may be either interleaved or noninterleaved. The choice is made by implementing a modification in the CPU.

#### 3.2.1.1. Noninterleaved Addressing of Main Storage

Noninterleaved addressing is provided only for a UNIVAC 1108 Unit Processor System (defined as a UNIVAC 1108 System which consists of one CPU and no IOC's) which has 65,536 or 131,072 words of main storage. In noninterleaved addressing, the main storage modules and the locations within each module are addressed sequentially. A Storage Unit cabinet containing two 32K modules is the minimum complement of main storage available. The maximum complement of 131K words of noninterleaved main storage is obtained by the addition of another cabinet containing 65K words of main storage. Table 3-1 shows the range of addresses for the locations in each main storage module.

| LOGICAL          | ADDRES        | S RANGES       |

|------------------|---------------|----------------|

| MODULE<br>NUMBER | OCTAL         | DECIMAL        |

| 0                | 000000-077777 | 0-32,767       |

| 1                | 100000-177777 | 32,768-65,535  |

| 2                | 200000-277777 | 65,536-98,303  |

| 3                | 300000-377777 | 98,304-131,071 |

Table 3-1. Octal and Decimal Address Ranges for Noninterleaved Main Storage Modules

A CPU can retrieve or store the operand of the current instruction, while simultaneously obtaining the next instruction from main storage (overlapping). If the operand for the current instruction and the next instruction word are in different modules, the CPU simultaneously requests main storage access for both the operand and the next instruction word (alternate module operation). If the operand for the current instruction and the next instruction word are in the same module of main storage, simultaneous access is not possible, and the CPU requests main storage access (read or write) for the operand first. After the operand has been transferred, the CPU requests main storage access to retrieve the next instruction word.

Figure 3-1 is a block diagram of a CPU with the maximum complement of noninter-leaved main storage. Since the desired efficiency of alternate module operation is obtained only when the instruction words and operands (data words) are not in the same main storage module, Main Storage Modules #0 and #1 in Figure 3-1 provide the minimum storage requirement for alternate module operation. Modules #2 and #3 provide expansion for the noninterleaved addressed main storage.

#### 3.2.1.2. Interleaved Addressing of Main Storage

The interleaved addressing method permits a more efficient use of main storage in the multiprocessor environment. Interleaved addressing is always used with a multiprocessor system and also with a unit processor system which has 196,608 or 262,144 words of main storage. When interleaved addressing is used, each processor (CPU or IOC) can address up to 262,144 main storage words.

When interleaved addressing is used, sequentially addressed main storage words within a 65K Storage Unit are located alternately in the two modules, even number addresses being in one 32K module and odd number addresses in the other.

Figure 3—1. Central Processor Unit with Maximum Noninterleaved Main Storage

At least two Storage Units (131,072 words) are necessary for interleaved addressing. Three or four Storage Units may be used, thereby expanding the capacity to 196K or 262K words. Table 3-2 shows the range of addresses for each module pair. Figure 3-2 shows a CPU with the maximum complement of interleaved addressed main storage.

| LOGICAL<br>MODULE | ADDRE         | SS RANGES       |

|-------------------|---------------|-----------------|

| PAIR<br>NUMBER    | OCTAL         | DECIMAL         |

| 0                 | 000000-177777 | 0-65,535        |

| 1                 | 200000-377777 | 65,536-131,071  |

| 2                 | 400000-577777 | 131,072-196,607 |

| 3                 | 600000-777777 | 196,608-262,143 |

Table 3—2. Octal and Decimal Address Ranges for Interleaved Main Storage Modules

Figure 3-3 shows a CPU and IOC of a UNIVAC 1108 Multi-Processor System with the maximum complement of interleaved main storage. The IOC requests access to main storage independently of the CPU. The IOC always provides for interleaved addressing of main storage.

Figure 1-1 shows a UNIVAC 1108 Multi-Processor System consisting of the maximum complement of interleaved addressed main storage with two IOC's and three CPU's. Each IOC and CPU has access to each main storage module by way of the MMA's.

The advantage of interleaved addressing is that it permits simultaneous access by two processors (CPU or IOC) to any odd address and any even address in a main storage module pair. The simultaneity of main storage accessing provides service under ideal conditions to a pair of access-requesting units at a rate which meets their needs without a perceptible decrease in overall operating speed for either unit.

#### 3.2.2. Multi-Module Access Unit (MMA)

The MMA is the interface between the two main storage modules of a 65K Storage Unit and a combination of IOC's and CPU's. The MMA includes switching and priority networks that provide access to each of two main storage modules for as many as two IOC's and three CPU's (IOC #0, IOC #1, CPU #0, CPU #1, and CPU #2).

The addition of the MMA Expansion Feature (F0879) expands the interface for that MMA to accommodate an additional CPU and IOC.

The MMA has two sections, one for each 32K main storage module of a Storage Unit. When an MMA receives an access request from an IOC or CPU for a main storage module which is not active, it initiates a cycle for that module. The MMA resolves conflicts caused by receipt of one or more additional access requests for that module within approximately 15 nanoseconds of the initial request.

When the MMA initiates a main storage cycle, the priority circuits associated with that module are activated to handle any access requests pending for that module at the time the cycle is initiated or any access requests received for that module during the current cycle.

Figure 3-2. CPU with Maximum Interleaved Main Storage

Figure 3—3. CPU, IOC, and Main Storage with MMA's for UNIVAC 1108 Multi-Processor System

If only one access request is pending when a cycle in a particular module is completed, the pending access request is serviced next. If access requests from two or more processors (CPU's or IOC's) are pending for a module just prior to completing a cycle in that module, the MMA's priority network determines which processor is serviced next, as follows:

- IOC's always have higher priority than CPU's.

- IOC #0 has higher priority than IOC #1.

- CPU #0 has higher priority than CPU #1 which in turn has higher priority than CPU #2.

Summarizing, the basic priority sequence for access to a main storage module is: IOC #0, IOC #1, CPU #0, CPU #1, and CPU #2 (highest to lowest priority).

Deviations from this basic priority scheme are as follows:

- If both IOC's are repetitively requesting access to a main storage module, priority alternates from IOC #0 to IOC #1 to IOC #0, etc; IOC #0 cannot monopolize the use of a main storage module to the exclusion of IOC #1. This occurs because the MMA priority circuits determine which IOC is to be granted access during the current main storage access cycle, that is, before the IOC currently being serviced can present another access request. If the two IOC's repetitively request access to the same module, however, access to that module by any of the CPU's is delayed until there is a break in the series of IOC access requests.

- If one or more CPU's request access to a main storage module while that module is servicing an IOC, and the other IOC is not requesting access, the highest priority CPU (considering lockout discussed below) will gain access next. The MMA priority circuits determine which processor will be serviced next before the completion of the current servicing cycle, that is, before the active IOC can present another access request for that module.

It is not possible for a CPU to monopolize the use of a main storage module to the exclusion of a lower priority CPU. The priority network modifies the basic priority scheme to prevent this by setting and clearing lockouts, as follows:

- Set Lockout for CPU #0: During each cycle servicing an access request from CPU #0, a lockout is set to inhibit initiation of a subsequent cycle for CPU #0 in the main storage module if either CPU #1 or CPU #2 has a pending access request for that module.

- Clear Lockout for CPU #0: If the lockout is set for CPU #0, it is cleared during any subsequent cycle in the module when CPU #1 is serviced provided there is no pending access request for that module from CPU #2. It is also cleared during any subsequent cycle in the module servicing CPU #2.

- Set Lockout for CPU #1: During each cycle servicing an access request from CPU #1, a lockout is set to inhibit initiation of a subsequent cycle for CPU #1 in the module if and only if CPU #2 has a pending access request for that module.

- Clear Lockout for CPU #1: If the lockout is set for CPU #1, it is cleared during any subsequent cycle when that module is used to service CPU #2.

#### 3.2.3. Main Storage Special Address Assignments

There are two special categories of main storage addresses. These are main storage addresses  $0_8$  through  $177_8$ , and a set of main storage addresses with fixed assignments.

#### 3.2.3.1. Hidden Storage

The control registers are assigned the same addresses as main storage locations  $0_8$  through 1778. If data is written into or read from a location whose operand address is less than  $200_8$ , the data is transferred to or from that addressed location in the control registers rather than to or from a location in main storage except as noted in the following paragraph. Thus, locations  $0_8$  through 1778 in main storage are somewhat protected and are referred to as hidden storage.

Information is read from locations in hidden storage rather than from the control registers in the following instances:

- The address is that of an instruction defined by the contents of the Program Address Counter (P register).

- The address is that of a word to be referenced as part of an indirect addressing sequence.

- The address is that of an instruction word referenced by an Execute instruction.

Information can be read from or written into hidden storage through data transfers performed by an I/O operation. (An I/O operation never transfers data to or from the control registers.)

#### 3.2.3.2. Fixed Address Assignments

The interrupt subroutine entrances and status words are assigned fixed locations in main storage as shown in Table 3-3. The values for bits 15, 16, and 17 of the addresses listed in Table 3-3 are represented by a X, Y, or Z in the address.

The value X is the contents of the Memory Select Register (MSR), which may be manually loaded by depressing the desired combination of the three MSR switches on the maintenance panel. It can also be loaded under program control by performing the Select Interrupt Location instruction. In a system with noninterleaved addressing and the maximum complement of 131,072 words of main storage, the only values permitted in the MSR are 0, 1, 2, or 3 (see Table 3-4). In a system with interleaved addressing and the maximum complement of 262,144 words of main storage, the only values permitted in the MSR are 0, 2, 4, or 6 (see Table 3-5). When an initial load operation is performed, the value in the MSR identifies the main storage module or module pair in which the incoming data is to be stored. During an ESI-I/O operation using the CPU's I/O section, the value in the MSR identifies the main storage module or module pair from which the ESI access control words are obtained.

The value Y is determined from the contents of the Last Address Register (LAR) ORed with the settings of the leftmost three Last Address switches on the CPU's maintenance panel as explained in 8.3.1.3. The value A is 3 or 7 depending on the setting of the rightmost Last Address switch on the CPU's maintenance panel.

| ADDRESS<br>(OCTAL)                   | ASSIGNMENT                                                                                                                                                                                 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X00200<br>X00201<br>X00202<br>X00203 | CPU #0 External Interrupt Status Word<br>CPU #1 External Interrupt Status Word<br>CPU #2 External Interrupt Status Word<br>Unassigned                                                      |

| X00204<br>X00205<br>X00206<br>X00207 | Unassigned<br>Unassigned<br>Unassigned<br>Unassigned                                                                                                                                       |

| X00210<br>X00211<br>X00212<br>X00213 | Power Loss Interrupt ESI Access Control Word Parity Error Interrupt ISI Access Control Word Parity Error Interrupt I/O Data Parity Error Interrupt                                         |

| X00214<br>X00215<br>X00216<br>X00217 | Unassigned<br>Unassigned<br>Day Clock Input<br>Day Clock Interrupt                                                                                                                         |

| X00220<br>X00221<br>X00222<br>X00223 | ISI Input Monitor Interrupt ISI Output Monitor Interrupt ISI Function Monitor Interrupt ISI External Interrupt                                                                             |

| X00224<br>X00225<br>X00226<br>X00227 | ESI Input Monitor Interrupt ESI Output Monitor Interrupt Unassigned ESI External Interrupt                                                                                                 |

| X00230<br>X00231<br>X00232<br>X00233 | External Interrupt Status Word for CPU Type 3011–99 Real Time Clock Interrupt Interprocessor Interrupt #0 Interprocessor Interrupt #1                                                      |

| X00234<br>X00235<br>X00236<br>X00237 | Unassigned  Main Storage Parity Error Interrupt, Mem 2  Main Storage Parity Error Interrupt, Mem 3  Main Storage Parity Error Interrupt, Mem 4  Main Storage Parity Error Interrupt, Mem 4 |

| X00240<br>X00241<br>X00242<br>X00243 | Control Register Parity Error Interrupt<br>Illegal Instruction Fault Interrupt<br>Executive Return Interrupt<br>Guard Mode/Storage Limits Protection Fault Interrupt                       |

| X00244<br>X00245<br>X00246<br>X00247 | Test and Set Interrupt Floating-Point Characteristic Underflow Fault Interrupt Floating-Point Characteristic Overflow Fault Interrupt Divide Fault Interrupt                               |

| X00250<br>X00251<br>X00252<br>X00253 | Unassigned<br>Unassigned<br>Unassigned<br>Unassigned                                                                                                                                       |

| X00254<br>X00255<br>X00256<br>X00257 | Unassigned<br>Unassigned<br>Unassigned<br>Unassigned                                                                                                                                       |

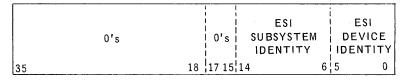

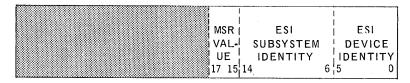

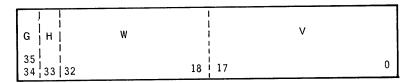

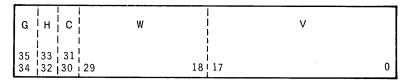

| Z00260)<br>Z00377)                   | IOC External Interrupt Status Word Locations                                                                                                                                               |